| epYme documentation |

|

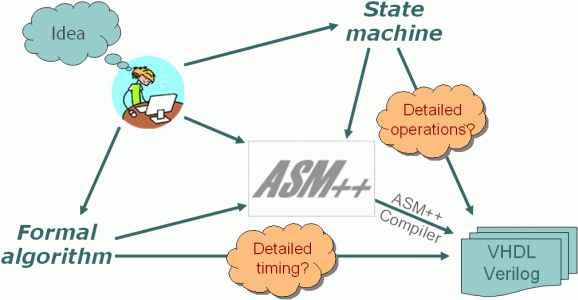

ASM++: a modern Algorithmic State Machine methodology for RTL designs

Index

Introduction

The ASM++ graphical language

is based on traditional Algorithmic State Machines (ASM charts),

defined by Tom Osborne and Christophe R. Clare in the mid-70's [1].

ASM++ charts increase their possibilities and they are used to develop complex RTL circuits, mainly for FPGA.

Using ASM++ charts it is possible to fully describe any cycle-driven RTL circuit:

it allows synchronous and asynchronous signals,

vectors and matrices, several execution threads on each module synchronized using one or several clocks,

several modules can be included on a MS Visio file, and several files can be managed on any design.

After processing, the ASM++ Compiler generates standard VHDL or Verilog codes

ready for simulation using ModelSim® and synthesis using Xilinx® ISE or Altera® Quartus II.

|

The ASM++ Compiler has been developed by epYme workgroup

at the University of Valladolid, Spain,

in cooperation with eZono AG (Jena, Germany)

and ISEND SA (Valladolid, Spain),

with financial support from the Spanish Government (MCIINN) using FEDER funds.

This document explains how to use the ASM++ charts and the ASM++ Compiler through several examples.

For any question or comments, please send an e-mail to Santiago de Pablo at sanpab@eis.uva.es.

Index · Next: Traditional ASM charts

|

|