| epYme documentation |

|

ASM++: a modern Algorithmic State Machine methodology for RTL designs

Compiler syntax

|

On these charts, all operations and conditions are expressed using either VHDL or Verilog hardware description languages.

This HDL symbiosys improve designer's productivity, because HDL expressions are easy to learn and ASM++ charts

allow designers to decide when and where they want to locate their operations.

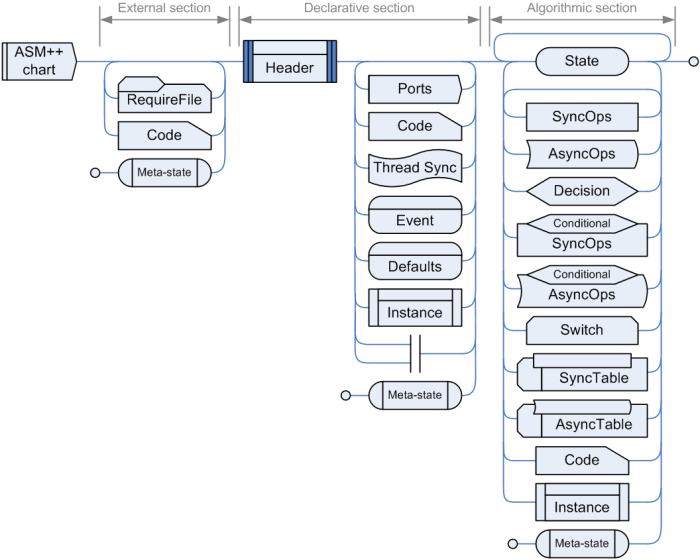

When using VHDL designers must follow the syntax expressed through the following trumpet diagram [2]:

Index · Previous: ASM++ Compiler · Next: Advanced compiler features

|

|